# Design and Performance of the Silicon Pixel Detector Modules for the CMS Experiment

## Dissertation

zur Erlangung der naturwissenschaftlichen Doktorwürde (Dr. sc. nat.)

vorgelegt der Mathematisch-naturwissenschaftlichen Fakultät der Universität Zürich

von

Christoph Hörmann aus Deutschland

Promotionskomitee

Prof. Dr. Claude Amsler (Vorsitz) Dr. Roland Horisberger

Zürich 2006

# Zusammenfassung

Der LHC Beschleuniger (Large Hadron Collider) ist ein ringförmiger Proton-Proton Beschleuniger, der zur Zeit am Europäischen Zentrum für Teilchenphysik (CERN) in Genf gebaut wird. Die Schwerpunktsenergie der kollidierenden Protonen wird 14 TeV sein, bei einer geplanten Luminosität von 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>. Die Datennahme soll im Herbst 2007 mit einem Probelauf bei einer niedrigeren Luminosität beginnen. Mit dem LHC wird es möglich sein, Teilchenphysik im Energiebereich von TeV zu betreiben. Das physikalische Meßprogramm umfaßt weitergehende Studien betreffend der Gültigkeitsgrenzen des Standard Modells (SM) und die Suche nach neuen physikalischen Erkenntnissen jenseits des SM. Den Schwerpunkt bildet jedoch die Entdeckung des Higgs Bosons. Viele Ereignisse werden b-Jets enthalten, die für die Identifikation der Zerfallskanäle mit top Quarks oder Higgs Bosonen dienen. Um die effiziente Erkennung dieser b-Jets zu ermöglichen, müssen die Flugbahnen der Zerfallsprodukte mit hoher Präzision bestimmt werden, um die Streuparameter zu ermitteln. Dafür müssen die innersten Lagen der Spurdetektoren so nah wie möglich am Wechselwirkungspunkt liegen, was eine hohe Strahlenbelastung bedeutet. Um Vielfachstreuung, die das räumliche Auflösungsvermögen verschlechtert, an den Detektorlagen zu vermeiden, muß die eingebaute Materialmenge minimal sein.

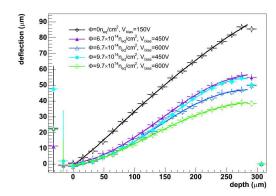

Der CMS (Compact Muon Solenoid) Detektor ist eines von den zwei großen Vielzweckexperimenten, die momentan am LHC aufgebaut werden. Die hohe Spurdichte im Bereich nahe des Wechselwirkungspunktes erfordert stark segmentierte Siliziumdetektoren, um die Spuren auflösen zu können und die Rate vernünftig niedrig zu halten. Die drei innersten Lagen des zentralen Spurdetektors, bestehend aus ungefähr 800 Modulen, und jeweils zwei Lagen in Vorwärtsrichtung, werden mit Silizium Pixeldetektoren ( $\sim 66 \times 10^6$  Pixel) ausgestattet sein. Sie liefern 3-dimensionale Raumpunkte und tragen somit zu einer effizienten Spurrekonstruktion auch unter hohen Raten bei. Die Pixelgröße ist 100 µm × 150 µm ( $r\phi \times z$ ) mit einer räumlichen Auflösung im Bereich von 15 µm. Sie hängt von der Bestrahlungsdosis und der Position im Pixeldetektor ab. Der Sensor und die Auslesechips (ROC = Readout Chip) bleiben voll funktionsfähig bis zu einer akkumulierten Strahlendosis von  $6 \times 10^{14}$  n<sub>eq</sub>/cm<sup>2</sup>. Dies entspricht den ersten vier Jahren des LHC Betriebes für die innerste Detektorlage.

In dieser Arbeit sind der Aufbau und die Leistungsmerkmale der Module für den zentralen zylinderförmigen Teil des CMS Pixeldetektors einschließlich der Funktionsweise der Komponenten beschrieben.

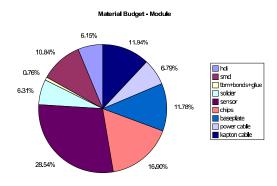

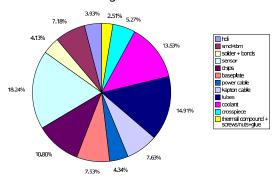

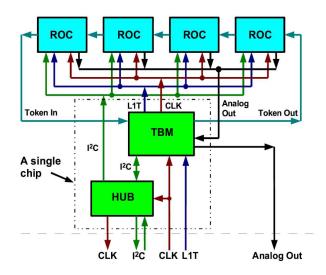

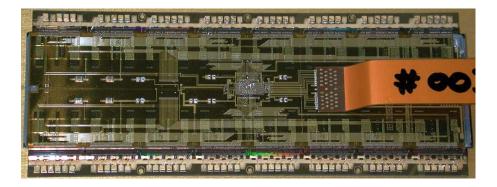

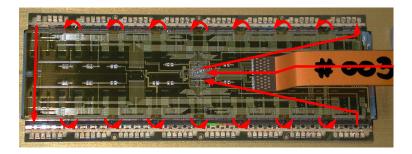

Die Module bestehen aus 16 Auslesechips, deren Kanäle einzeln mit den 66560 Pixeln des Sensors, mittels einer eigens entwickelten Technik, verbunden sind. Spezielle Signal- und Stromkabel verbinden die Module mit der Steuer- und Ausleseelektronik. Auf dem Modul werden die Signale und die Spannungen von einer flexiblen, sehr leichten Leiterplatte zu den

ROCs verteilt. Diese Leiterplatte (HDI = High Density Interconnect) ist mit dem Token Bit Manager Chip (TBM) bestückt, der die Auslese des Moduls organisiert. Zur mechanischen Versteifung der Modulstruktur ist sie auf zwei Trägerstreifen geklebt. Insgesamt beläuft sich die Materialmenge eines Moduls auf 1.2 % einer Strahlungslänge, beziehungsweise 1.6 % einschließlich der mechanischen Struktur und der Kühlflüssigkeit. Die Konstruktion des Moduls wurde bestimmt durch die physikalischen Anforderungen sowie auch durch die extremen Betriebsbedingungen.

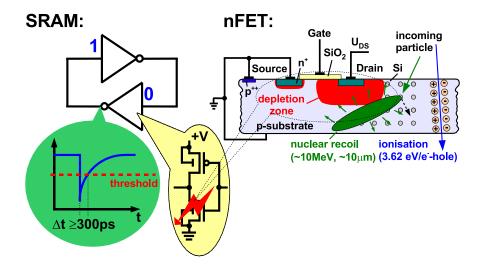

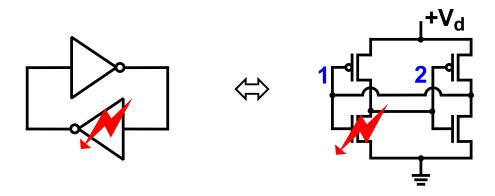

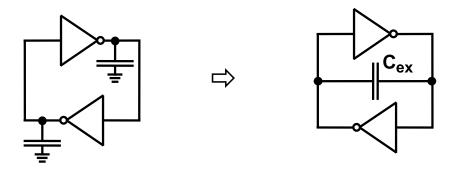

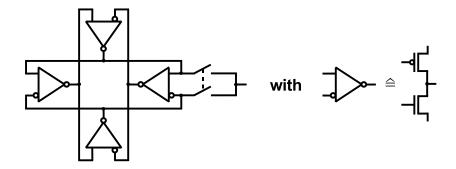

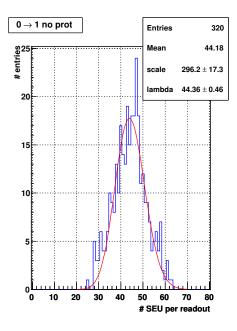

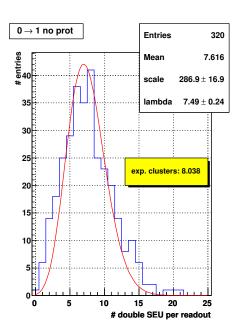

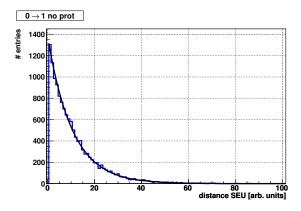

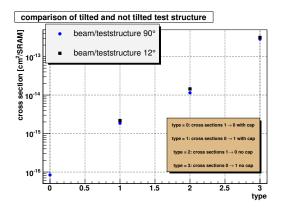

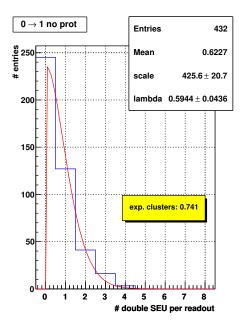

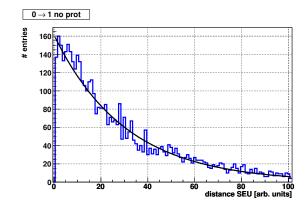

Der starke Strahlungsuntergrund verursacht nicht nur eine allmähliche Änderung der Charakteristik des Auslesechips, sondern korrumpiert auch die Ausleseelektronik. Eine Folge davon sind unkontrolliert veränderte Speicherzellen-Inhalte (SEU = Single Event Upsets), die ein ernstes Problem für den Betrieb des Pixeldetektors darstellen. Für die Untersuchung der SEU Problematik wurden Testschaltkreise mit Schieberegistern, bestehend aus Speicherzellen (SRAM = Static Random Access Memory) wie sie im ROC verwendet wurden, mit und ohne Schutzkapazität entwickelt und hergestellt. Der SEU Wirkungsquerschnitt der Teststrukturen und eines Auslesechips (ROC PSI46V1) wurden bei Strahltests bestimmt. Die gemessenen SEU Wirkungsquerschnitte für geschützte Speicherzellen sind  $2.57 \times 10^{-16}$  cm<sup>2</sup>/SRAM für einen Übergang von  $0\rightarrow 1$  und  $0.529\times 10^{-16}$  cm<sup>2</sup>/SRAM für eine Änderung von  $1\rightarrow 0$ . Die Verbesserung bedingt durch die Schutzkapazität beläuft sich mindestens auf einen Faktor 100 und hängt vom ursprünglich gespeicherten Zustand ab. Mit den gemessenen Wirkungsquerschnitten ergibt sich eine SEU Rate pro Kontrollnetzwerk für die innersten zwei Lagen von weniger als 0.03 Hz. Durchschnittlich wird es ungefähr 8 Stunden dauern, um 1\% aller Speicherzellen, die von einem Kontrollnetzwerk bedient werden, zu korrumpieren. Dies ergibt ca. 1 SEU pro Sekunde für den gesamten zentralen Teil des Pixeldetektors ( $\sim 48 \times 10^6$  Pixel). Deswegen kann auf ein wiederholtes Programmieren der Speicherzellen während der Datennahme höchstwahrscheinlich verzichtet werden.

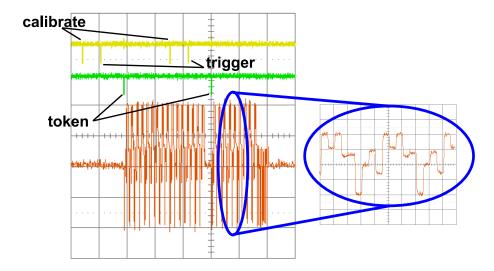

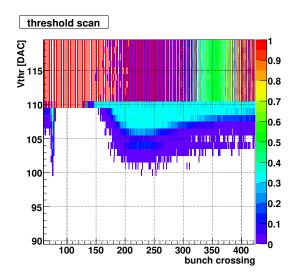

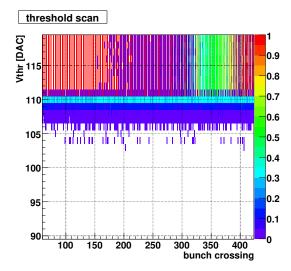

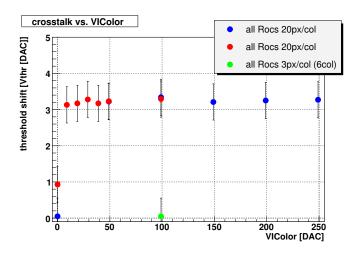

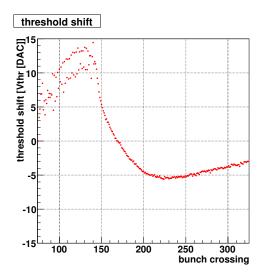

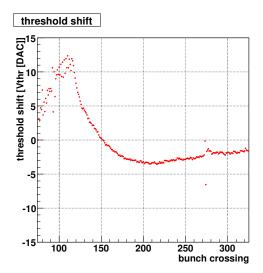

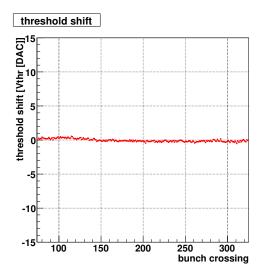

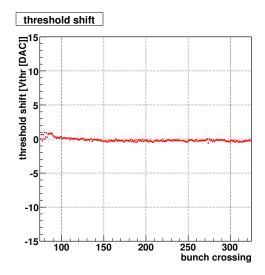

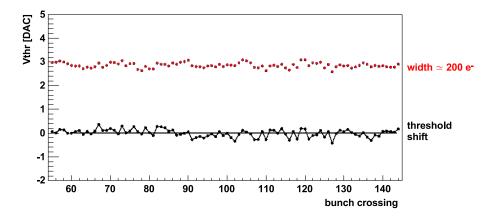

Der Pixeldetektor muß permanent Daten nehmen und gleichzeitig ausgelesen werden können, um die Totzeit minimal zu halten und eine maximale Effizienz bei einer bestimmten globalen Komparatorschwelle zu erreichen. Um dies zu garantieren, muß das elektronische Übersprechen auf dem Modul so gering wie möglich sein. Das gemessene Übersprechen hängt von der Anzahl getroffener Pixel und dem Zustand des Auslesevorgangs ab. Für Protonkollisionen wurde eine Verschiebung der globalen Schwelle um ca. 200 Elektronen gemessen. Sogar für den Fall von Ionenkollisionen, mit der entsprechend höheren Anzahl von getroffenen Pixeln, ergibt sich eine Verschiebung der Schwelle von weniger als 300 Elektronen. Verglichen mit einer globalen Komparatorschwelle von 2500 Elektronen, die das Entwicklungsziel des Pixeldetektors ist, ist das gemessene Übersprechen tolerabel.

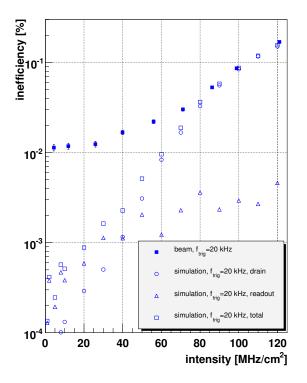

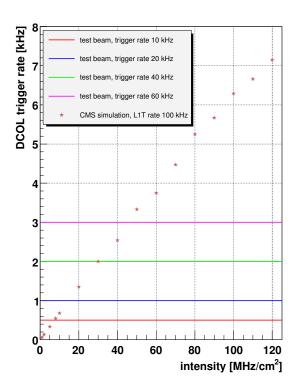

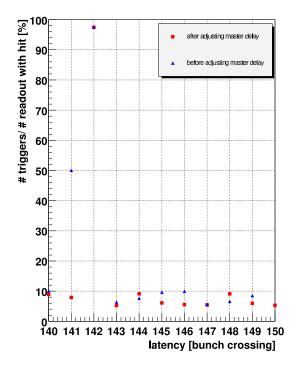

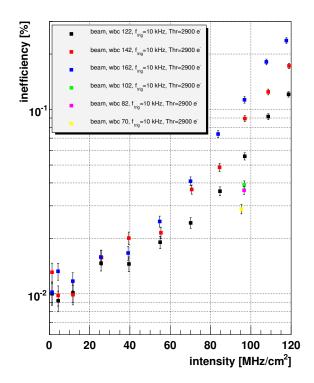

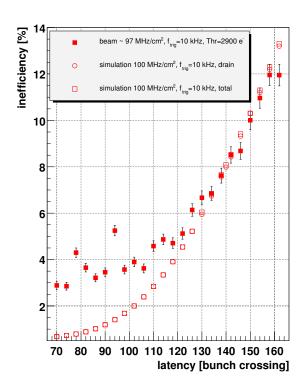

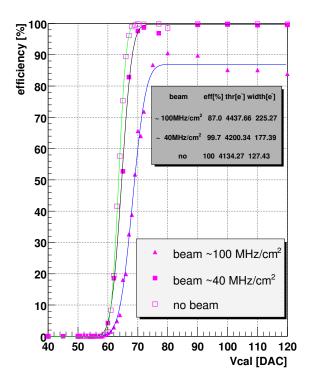

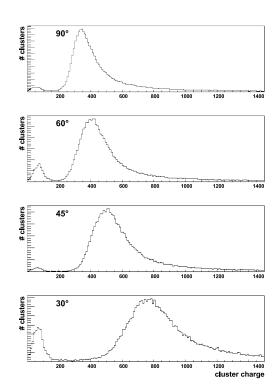

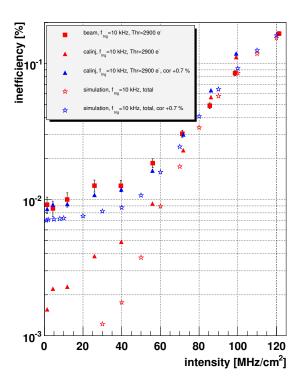

Die Ineffizienz des Pixeldetektors muß über den gesamten Spurdichtenbereich, der unter LHC ähnlichen Bedingungen erwartet wird, minimal sein. Um dies zu testen, wurde ein Pixeldetektor Modul zum ersten mal unter LHC ähnlichen Bedingungen in einem hoch-raten Pionenstrahl betrieben. Das Zusammenspiel zwischen dem TBM und den 16 ROCs funktionierte problemlos. Die gemessene Ineffizienz konnte mit der auf den Strahltest angepaßten Simulation reproduziert werden. Daher scheinen die Datenverluste in der Simulation korrekt berücksichtigt zu sein. Auf reale CMS Bedingungen angewandt, ergibt sie eine Ineffizienz von 3.8 % für die innerste Lage bei einer Triggerrate von 100 kHz. Die niedrigste globale Komparatorschwelle für einen stabilen Betrieb des Moduls im Strahltest war 2000 Elektronen.

Da die Leistungscharakteristik der Module die Anforderungen erfüllt, hat die Serienproduktion mit dem in dieser Arbeit beschriebenen Aufbau der Module bereits begonnen. Das angestrebte Ziel der Produktion sind 4 Module pro Tag. Nachdem ungefähr 400 Module für die 4 cm und die 7 cm Lage hergestellt sein werden und die Inbetriebnahme des zentralen Teils des Pixeldetektors erfolgt ist, werden die ersten Messungen Ende 2007 beginnen.

# Abstract

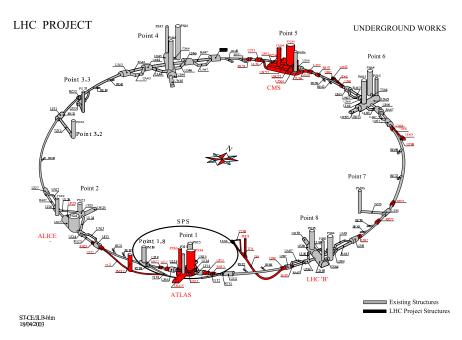

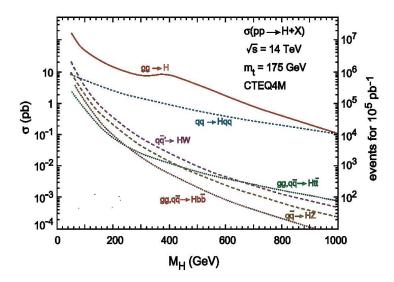

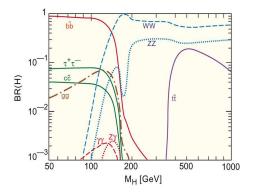

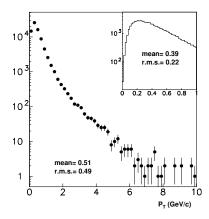

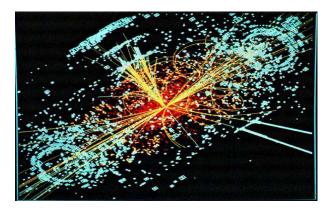

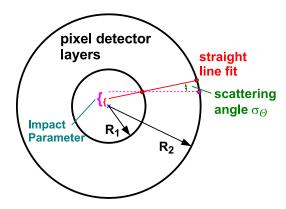

The Large Hadron Collider (LHC) is a circular proton-proton collider currently under construction at the European Organization for Nuclear Research (CERN) in Geneva. The center-of-mass energy will be 14 TeV with a design luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. The scheduled start-up for taking data with a low luminosity pilot run is late 2007. The LHC will allow to explore new physics at the TeV scale with a physics program including investigations of the limits of the Standard Model (SM) and the search for physics beyond the SM. The focus lays on the search for the Higgs boson. Many interesting events contain b-jets which will be used to identify physics channels with top quarks or the Higgs boson. In order to allow an efficient recognition of these b-jets, trajectories of the reaction products have to be measured with high precision to determine the impact parameter. Therefore the tracking has to extend as closely as possible towards the interaction point. This results also in a high integrated radiation dose for the innermost layer. To reduce multiple scattering effects which downgrade the spatial resolution the amount of material must be minimal.

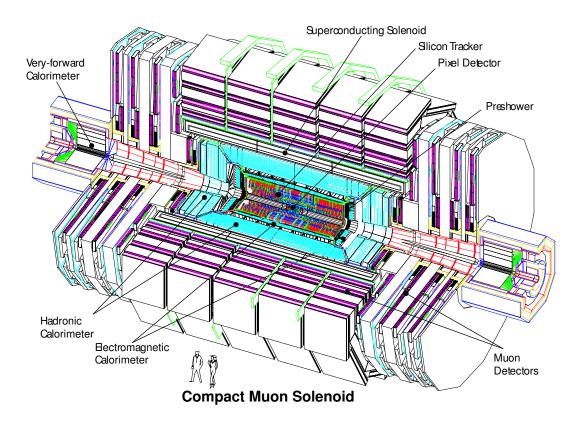

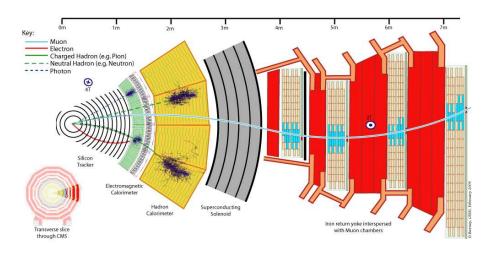

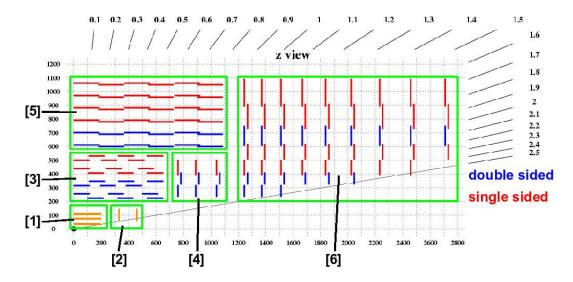

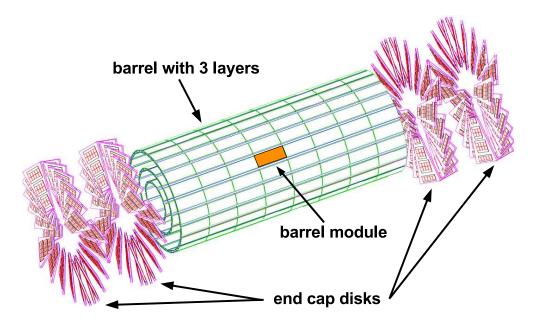

The Compact Muon Solenoid (CMS) detector is one of the two large multi purpose experiments which are being installed at the LHC. The high track density in the region close to the interaction point requires highly segmented silicon detectors to separate the tracks and to keep the occupancy low. The three innermost tracking layers composed of about 800 modules and two sets of forward disks will be equipped with hybrid silicon pixel detectors ( $\sim 66 \times 10^6$  pixels). They provide true 3-dimensional space point information and will contribute to an efficient track reconstruction even under high rate conditions. The pixel size is  $100~\mu m \times 150~\mu m~(r\phi \times z)$  and the spatial resolution is in the range of 15  $\mu m$  depending on the irradiation fluence and the position in the pixel detector. The sensor and the readout chips remain fully operational until  $6 \times 10^{14}~n_{\rm eq}/{\rm cm}^2$  corresponding to the first four years of LHC operation for the innermost layer.

In this thesis the design and the performance of the modules for the barrel of the CMS pixel detector including the functionality of their components is described.

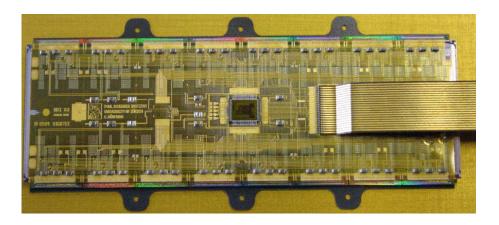

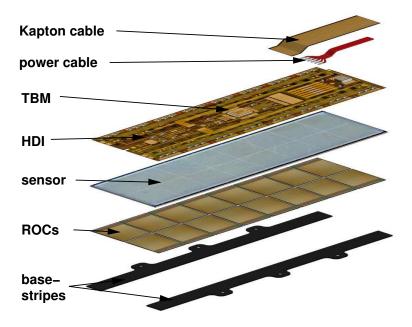

The modules are composed of 16 Readout Chips (ROCs) connected to the sensor segmented into 66560 pixels by a dedicated bump bonding technique. The control signals and the power are supplied to the module by the control cable and the power cable. On the module the signals and the power are distributed to the ROCs by a flexible, low mass printed circuit board. This High Density Interconnect (HDI) is equipped with the Token Bit Manager (TBM) chip which organizes the readout of the module. For the mechanical fixation the sandwich structure is glued to the base stripes. In total the amount of material sums up to about 1.2 % of a radiation length and to 1.6 % including the support structure and the coolant. The design of the module components was directed by the physics requirements, but

also by the challenging operating conditions.

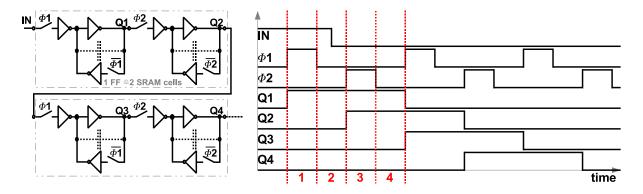

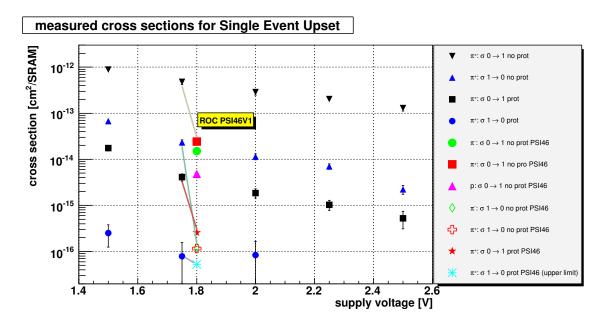

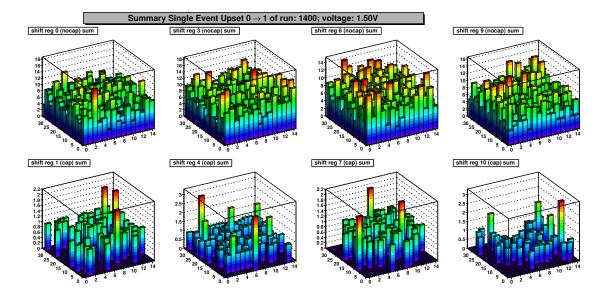

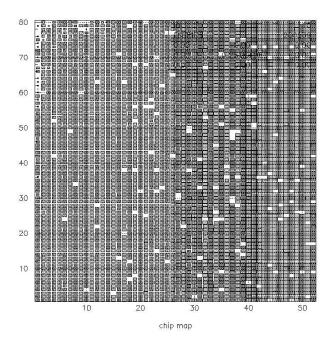

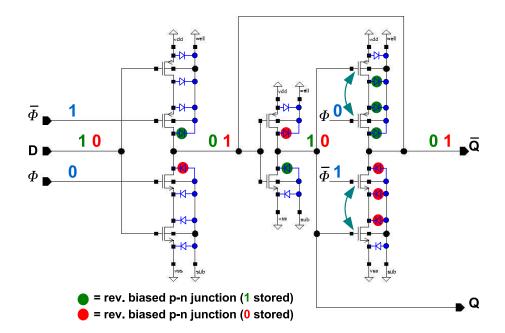

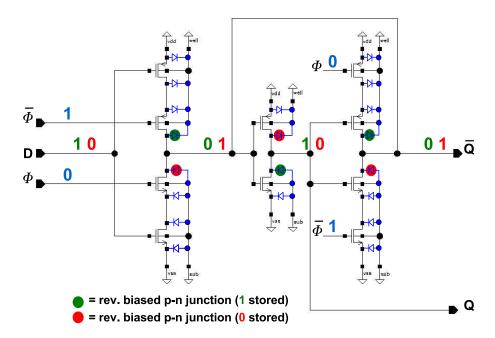

The harsh radiation environment causes not only a gradually change in the characteristic of the ROC but also Single Event Upsets (SEUs). The consequence of SEUs are instantaneously corrupted memory cells which are a serious operational problem for the pixel detector. For investigating the SEU problem test structures with shift registers consisting of Static Random Access Memory (SRAM) cells as used in the ROC with and without a protection capacitor were designed. The SEU cross sections of the SRAM cells and of a pixel readout chip (ROC PSI46V1) were determined in a beam test. The measured SEU cross sections for the protected storage cells are  $2.57 \times 10^{-16}$  cm<sup>2</sup>/SRAM for a transition from  $0\rightarrow 1$  and  $0.529 \times 10^{-16}$  cm<sup>2</sup>/SRAM for a changeover from  $1\rightarrow 0$ . The benefit of the protection capacitor is at least about a factor of 100 in the cross section and depends on the switching direction. With the measured cross sections the SEU rate per control network for the first and second layer is less than 0.03 Hz. In average it will take about 8 hours to switch 1%0 of all SRAM cells controlled by the corresponding digital optical link. This yields in about 1 SEU per second for the entire pixel detector barrel ( $\sim 48 \times 10^6$  pixels). Therefore reloading single pixel cells during the data taking period can be most likely avoided.

The pixel detector has to perform continuous data taking and simultaneous readout operation with minimal dead-time to achieve a maximum efficiency at a certain global threshold. To guaranty this the electronic crosstalk on the module must be as low as possible. The measured crosstalk depends on the cluster size and the states of the readout. For proton collisions the measured threshold shift is about 200 electrons. Even in the case of heavy ion collisions with the corresponding larger cluster sizes the threshold shift is smaller than 300 electrons. Compared to the global threshold of 2500 electrons which is the design goal of the pixel vertex detector the measured pickup is tolerable.

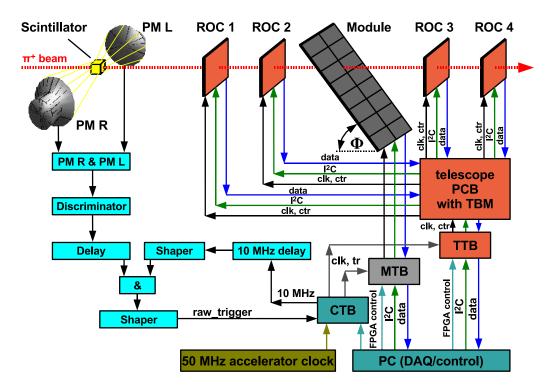

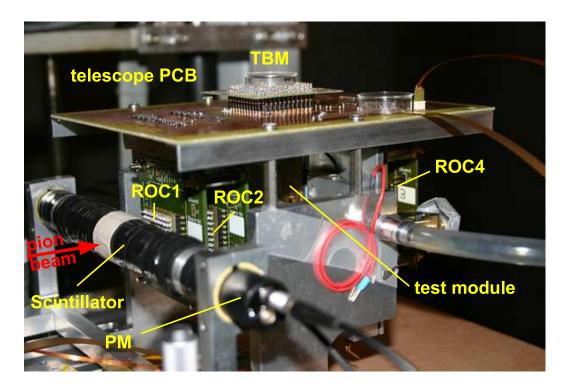

The detection inefficiency of the pixel detector must be minimal up to the expected track densities under LHC like conditions. To test the performance a pixel detector module was operated the first time under LHC like conditions in a high rate pion beam. No operational problem in the interaction of the 16 ROCs with the TBM was observed. The measured inefficiency could be reproduced with the simulation adapted to the beam test. The data losses seems to be described correctly in the simulation and applied to real CMS conditions an inefficiency of 3.8 % for the innermost layer and a level-1 trigger rate of 100 kHz is expected. The lowest global comparator threshold for a stable module operation in the beam test was about 2000 electrons.

Since the module performance fulfill the requirements the mass production of the modules has already started with the final design described in this work. The goal of the production is to assembly 4 modules per day. After the production of about 400 modules for the 4 cm and 7 cm layer and the successful commissioning of the barrel part of the pixel vertex detector, the first data-taking is expected for late 2007.

# Contents

| Zι | ısam  | nenfassung                                 | j            |

|----|-------|--------------------------------------------|--------------|

| A  | bstra | et                                         | $\mathbf{v}$ |

| C  | ontei | t e                                        | vii          |

| 1  | Intr  | oduction                                   | 1            |

| 2  | LH    | and CMS                                    | 3            |

|    | 2.1   | Large Hadron Collider at CERN              | 3            |

|    | 2.2   | Physics at the Large Hadron Collider       | 6            |

|    |       | 2.2.1 Higgs Boson                          | 7            |

|    |       | 2.2.2 Supersymmetry                        | 9            |

|    | 2.3   | Compact Muon Solenoid Experiment           | 9            |

|    |       | 2.3.1 Summary of Detector Requirements     | 9            |

|    |       | 2.3.2 CMS Subdetectors                     | 10           |

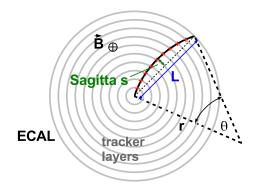

|    | 2.4   | Central Tracker of the CMS Experiment      | 15           |

|    |       | 2.4.1 Silicon Strip Detector               | 16           |

|    |       | 2.4.2 Pixel Vertex Detector                | 17           |

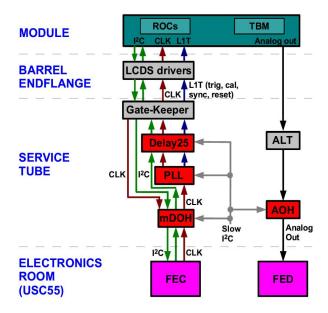

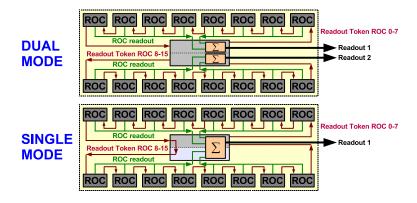

|    |       | 2.4.3 Readout and Control System           | 22           |

|    |       | 2.4.4 Performance                          | 23           |

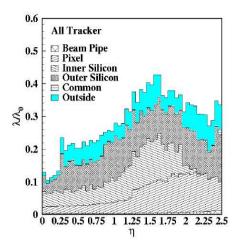

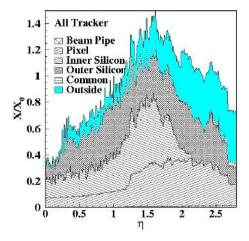

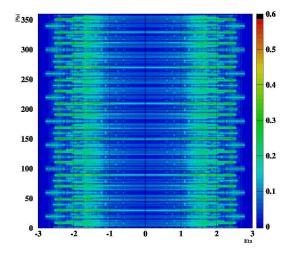

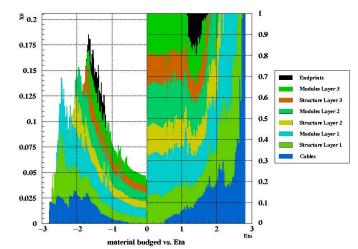

|    |       | 2.4.5 Material Budget                      | 26           |

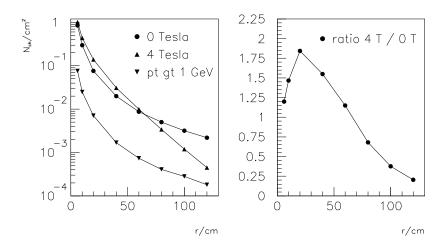

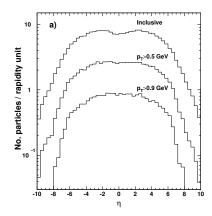

|    |       | 2.4.6 Radiation Levels                     | 28           |

|    | 2.5   | Trigger and Data Acquisition System of CMS | 28           |

|    | 2.6   | Summary                                    | 29           |

| 3  | Mo    | ule of the Pixel Vertex Detector           | 31           |

|    | 3.1   | Components of the Module                   | 32           |

|    |       | 3.1.1 Kapton Cable                         | 33           |

|    |       | 3.1.2 Power Cable                          | 33           |

|    |       | 3.1.3 Token Bit Manager Chip               | 33           |

|    |       | 3.1.4 High Density Interconnect            | 34           |

|    |       | 3.1.5 Sensor                               | 35           |

|    |       | 3.1.6 Readout Chip                         | 35           |

|    |       | 3.1.7 Bump Bonding                         | 35           |

|   |      | 3.1.8 Base Stripes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35         |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   | 3.2  | Silicon Sensor for the Modules of the Pixel Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36         |

|   |      | 3.2.1 Induced Charge and Radiation Dose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37         |

|   |      | 3.2.2 Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37         |

|   |      | 3.2.3 Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38         |

|   | 3.3  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12         |

|   | 3.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13         |

|   | 3.5  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15         |

| 4 | Rea  | dout Chip of the Pixel Vertex Detector 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u>1</u> 7 |

|   | 4.1  | Readout Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17         |

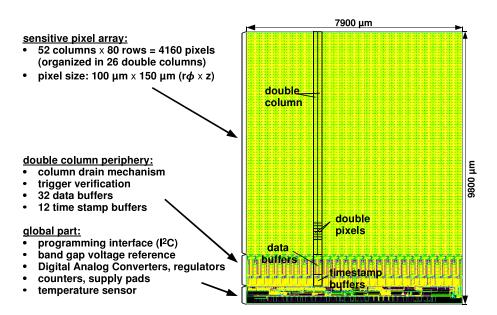

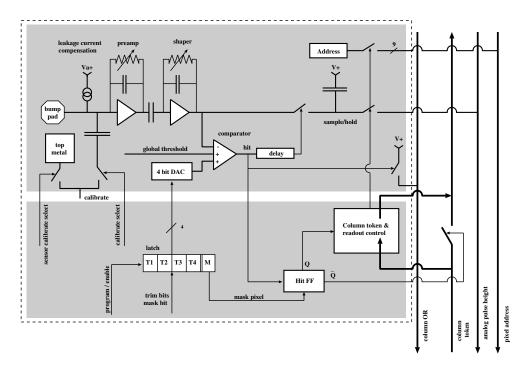

|   |      | 4.1.1 Pixel Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>1</b> 9 |

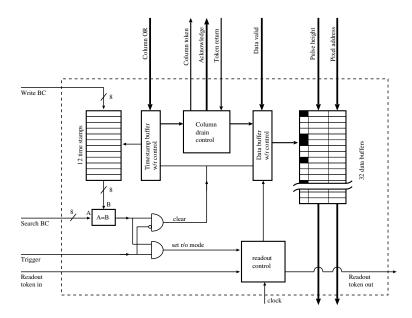

|   |      | ± v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51         |

|   |      | 4.1.3 Global Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52         |

|   |      | O Company of the comp | 53         |

|   | 4.2  | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54         |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55         |

|   |      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56         |

|   | 4.3  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58         |

| 5 | Sing | gle Event Effects in the Readout Chip 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>i</b> 1 |

|   | 5.1  | Single Event Upset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32         |

|   | 5.2  | Test Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37         |

|   | 5.3  | Beam Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38         |

|   |      | 5.3.1 Pion Beam Test with Test Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38         |

|   |      | 5.3.2 Proton Beam Test with the Readout Chip PSI46V1 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38         |

|   | 5.4  | Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36         |

|   |      | 5.4.1 Protection Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39         |

|   |      | 5.4.2 Asymmetry in Switching Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72         |

|   |      | 5.4.3 Comparison of $p$ and $\pi^-$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73         |

|   |      | 5.4.4 Multiple Bit Upset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73         |

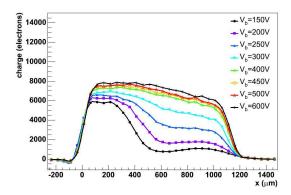

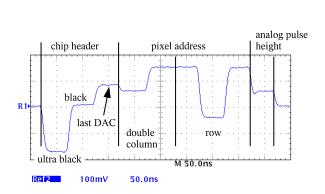

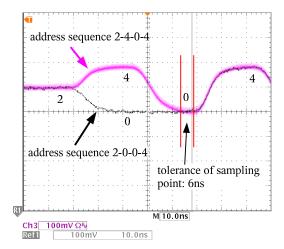

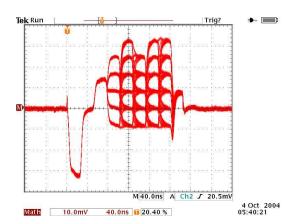

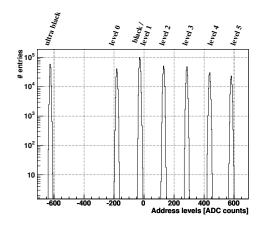

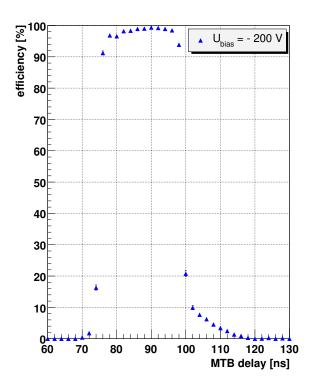

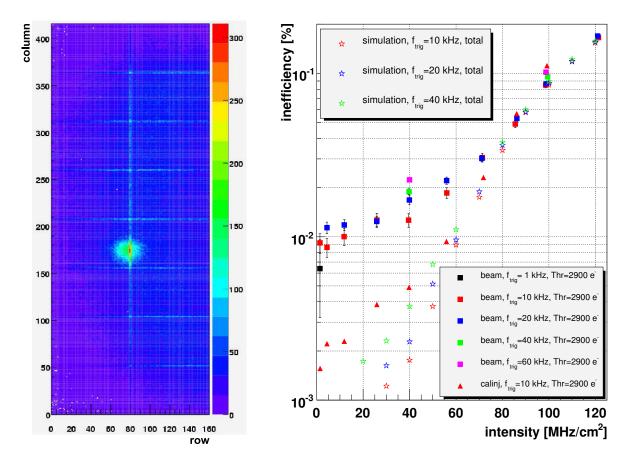

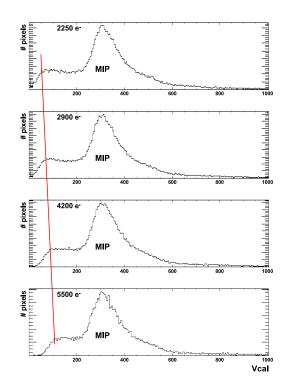

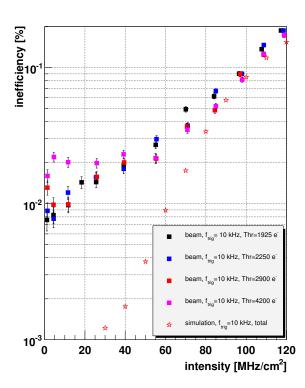

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75         |